|

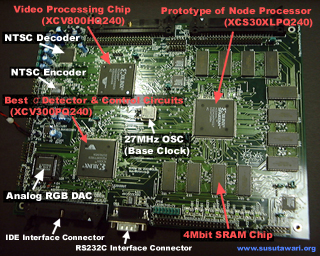

| 図.1 Photograph of Prototype Board. |

|---|

本研究はパターン認識処理とそのパラメータ学習の高速化を目的とするもので、 その主な手法はアルゴリズムのデジタル回路(ハードウェア)化とその並列化であ る。これにより従来のPC(パソコン)による処理に比べ数十〜数百倍以上の高速処 理が実現可能である。さらに我々の提案する新たなアーキテクチャを用いること で、ハードウェアでの並列化の際に問題となるピン・ボトルネックを抑えること ができ、低実装面積、低コストが実現できる。この結果、現実的なサイズ(デス クトップ・サイズ)で高速なパターン認識処理を行うことができる。 確率的ニューラルネットワーク(PNN)は別名、カーネルベース法ともよばれ、ベイズの 識別定理に基づいた、パターン認識アルゴリズムの一つで最近見直され始めてい る。このアルゴリズムは並列性が高いため、ハードウェアの並列度を高められれ ば、より高速な処理が可能となる。さらに本研究では認識処理よりもはるかに計 算量が多く、より高速な処理が期待される、認識パラメータ学習の高速化につい ても研究を進めている。

図.1に製作した試作基板の写真を示す。本試作基板は 試作基板としては2作目で、1作目でFPGA内で行っていたNTSCビデオ・コンポジッ ト信号のデコード/エンコードを専用チップを用いて行っている。これは今後利 用を考えているカラー信号に対応することが主な目的であるが、現在のところ輝 度情報のみを用いたパターン認識処理を行っている。FPGAは計3つ実装しており、 ビデオカメラから入力された画像より、モザイク・パターンの生成を行うプリプ ロセッサ(前処理部)、そのパターンの認識を行うノードプロセッサ(認識部)、 そして学習回路(Best Sigma Detector)及び全体の制御回路を搭載した学習/制 御部から構成されている。

|

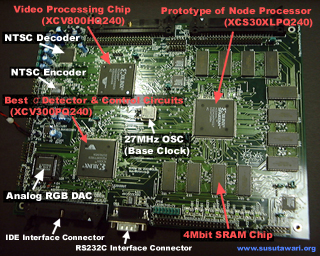

| 図.2 PNN System Configuration. |

|---|

この他にパターンデータを保存しておくためのハードディスク・インターフェー スやパソコンとデータや命令をやりとりするためのRS-232Cインターフェースな どを持っている。 図.2に全体の構成を示す。ビデオカメラから入力さ れた画像はOKI製のNTSCデコーダMSM7664TBで輝度値約8bit(シンクを含む)に量子 化(A/Dコンバート)されXilinx社のFPGA XCV800HQ240内に作成したプリプロセッ サに入力される。 プリプロセス(モザイク化等の処理)結果はAnalogDevices社のNTSCエンコーダを 経由してテレビモニタにてモニタリングできる。図.2中ではMax Detector, Best Sigma DetectorはXCV800にインプリメントされているが、現在はアーキテクチャ の細かな変更に伴い、XCS30XL及びXCV300にインプリメントしている。 このようなインプリメントの変更が容易に行えるのもFPGAならではである。

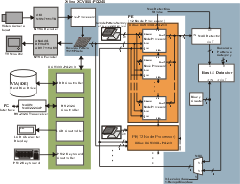

図.3に現在製作しているPNNハードウェアの回路構成を示す。この回路は並列に

多数実装することができるようにモジュール化されており、ここではこれを

Node Processorとよぶ。Node Processorの並列実装構成については図.2に示す通

りである。Node Processorは入力として、サンプルパターン、テストパターン、

そして核サイズ(パラメータσ)の3つ(それぞれ8bit幅)と、1つの出力を持つ。

ここで重要なのことは、サンプルパターン入力以外は全て他のNode Processorと

共通のバス接続となっていることである。これによりNode Processorの実装面で

の並列化が容易となっている。ところで、バス接続を用いることは時に時分割処

理を要求し、スケーラビリティの低下を招く。本アーキテクチャにおいてもNode

Processorの出力をバス接続とすることによって時分割処理を行うことになるが、

この処理の割合は、その前段の並列処理可能なNode Processor内の演算処理に比べ

はるかに小さいため、高いスケーラビリティを得られる。

次に、Node Processorの動作について述べる。図.3中でまず「Kernel Size

Adjuster」にて、メモリから読み込まれたサンプルパターンの1segmentの値に

σの値を加算、減算する。これによりサンプルパターンのこの1segmentの値は

図.3中左上のように、その値を中心にσ分の範囲を持つことになる。次に

「Kernel Size Comparator」にてこのσ分の範囲を持ったサンプルパターンと

位置的に対応するsegmantのテストパターンを比較し、全ての値がこの範囲内にあれ

ば"1"を、そうでなければ"0"を出力する。この"1"の数を後段のカウンタで数え、

これを時分割で外部のバスに出力する。この値が最も大きかったものがそのサン

プルに近いものと考えられ、そのサンプルの属するカテゴリがテストパターンの

カテゴリと言える。こうして未知のテストパターンが既知のいずれのカテゴリに

属するかを識別する。これはベイズの識別器そのものと言えよう。

|

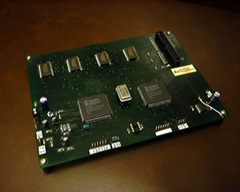

| 図.4 The 1st Prototype Board. |

|---|

図.4は第1作目のパターン認識ボード「SusuPRB」のプロトタイプで、エッチン グ処理、グリーンレジスト塗装をした手製の両面基板を使用している。FPGAは XILINX社のSpartanシリーズを 使用しており、他にSRAMとビデオ用のA/D,D/Aコンバータ、ATAハードディスク用 の40Pinコネクタを搭載している。このプロトタイプは白黒映像のみを想定していた ので特に外部に専用チップは用いず、NTSCのデコード/エンコードは外部の DAC,ADCとFPGAのみで行っている。

by すすたわり